数字电路笔记

逻辑运算

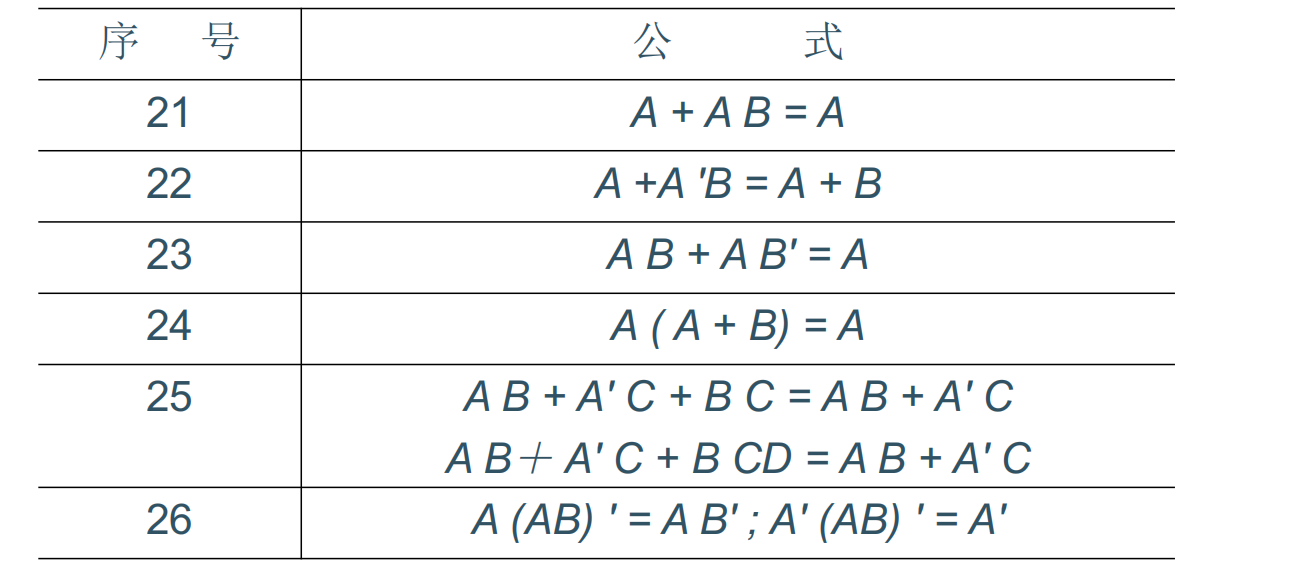

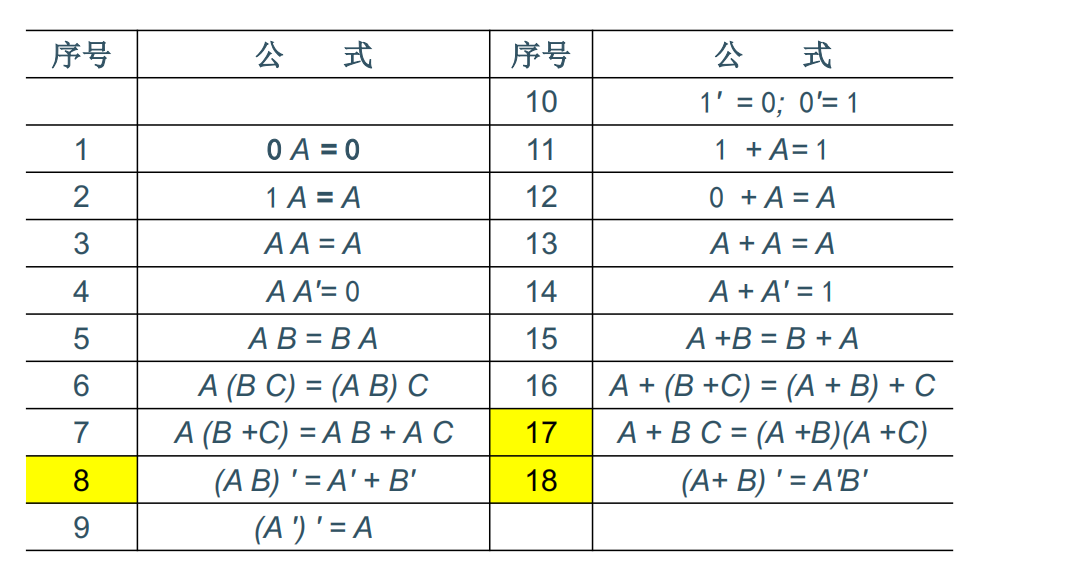

基本公式

基本定理

代入定理

反演定理

逻辑函数表示方法

- 真值表

- 逻辑式

- 将输入/输出之间的逻辑关系用与/或/非的运算式表示 就得到逻辑式

- 逻辑图

- 波形图

- 卡诺图

标准形式

逻辑函数化简

公式法

- 用卡诺图表示逻辑函数

- 找出可合并的最小项

- 化简后的乘积项相加

约束项

在逻辑函数中,对输入变量取值的 限制,在这些取值下为1的最小项称 为约束项

任意项

在输入变量某些取值下,函数值为1或 为0不影响逻辑电路的功能,在这些取 值下为1的最小项称为任意项

常用编码

补码反码

反码

负数补码为反码+1

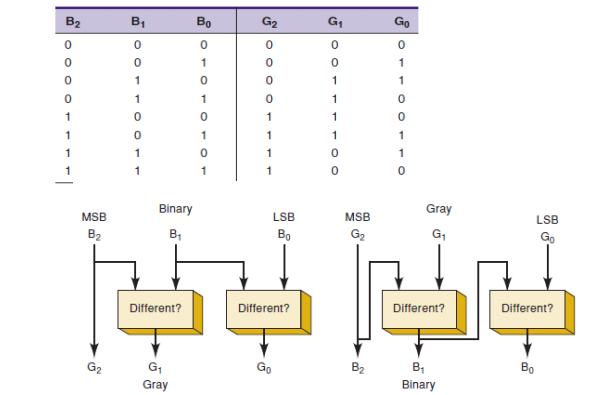

格雷码

组合逻辑

特点

- 任意时刻输出仅取决于输入,没有反馈

- 不含存储单元

编码器

普通编码器

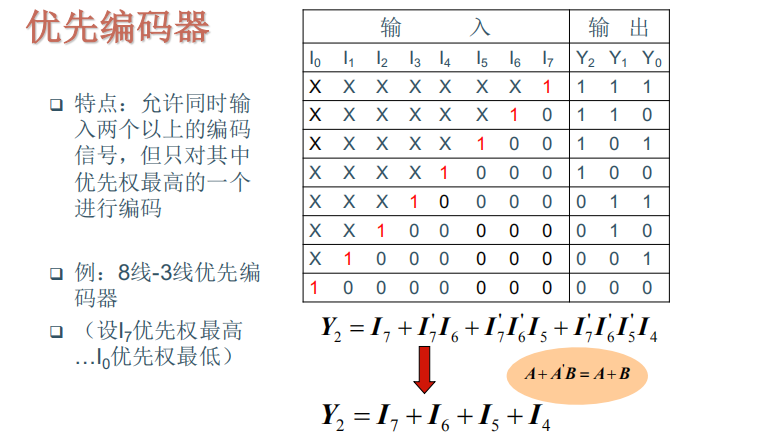

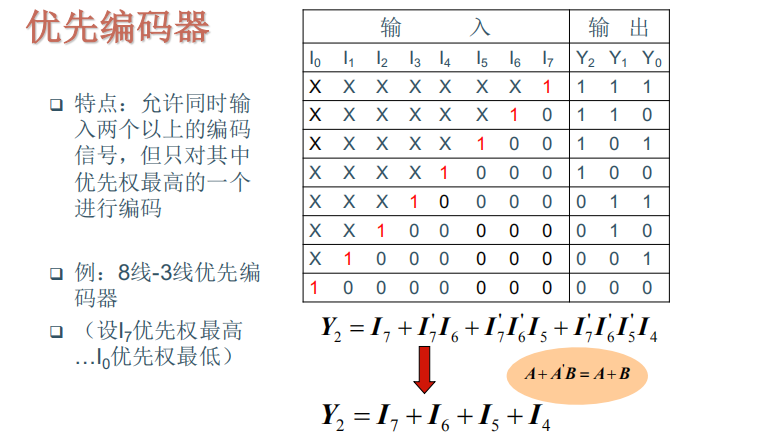

优先编码器

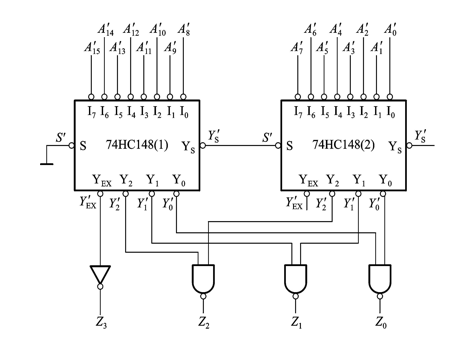

两片编码器合并

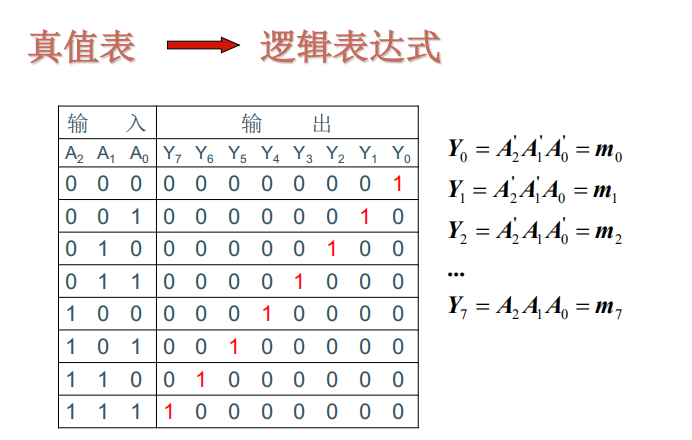

译码器

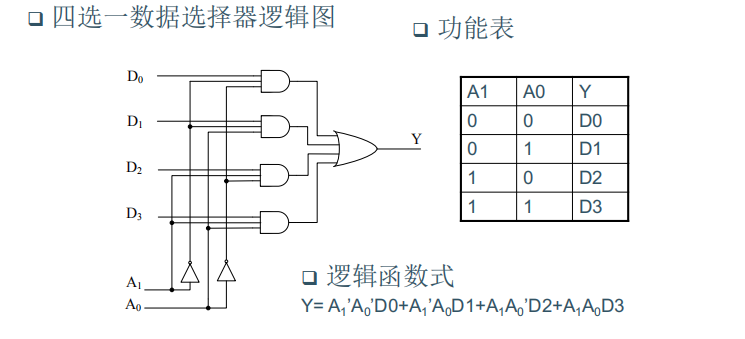

数据选择器

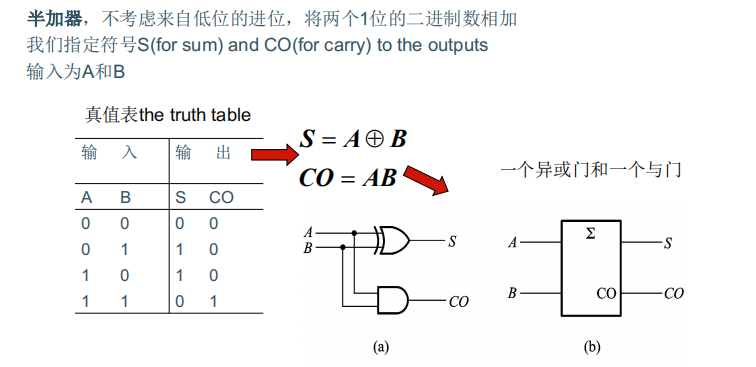

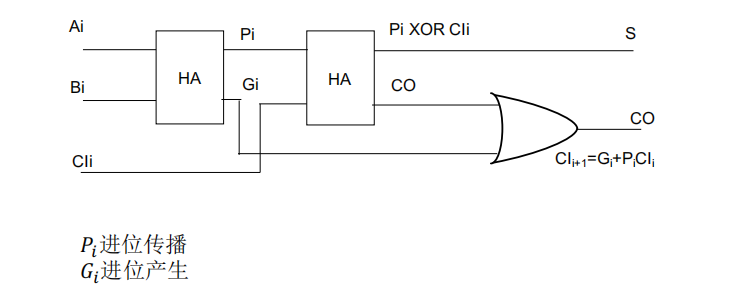

半加器

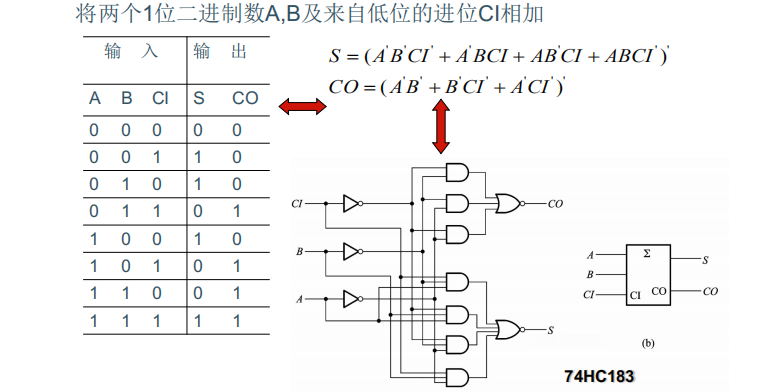

全加器

用半加器实现全加器

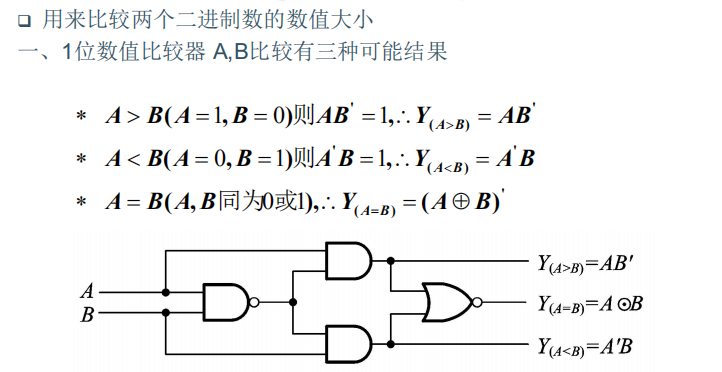

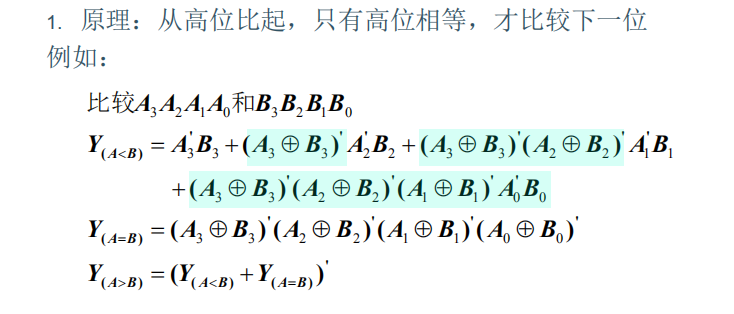

数值比较器

多位数值比较器

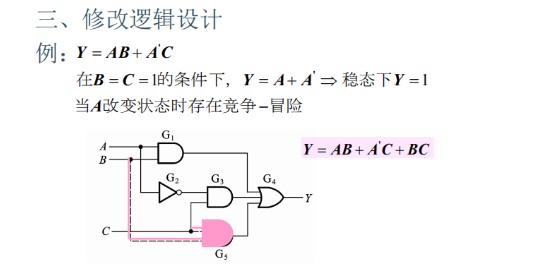

组合电路的竞争和冒险

增加冗余项可以消除改现象

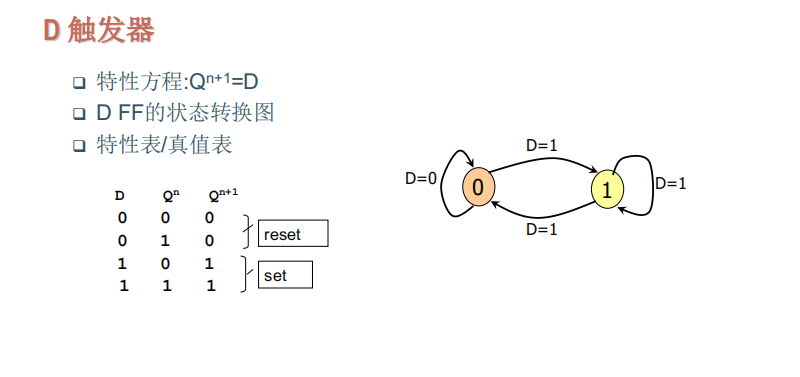

触发器

如何存储数据?

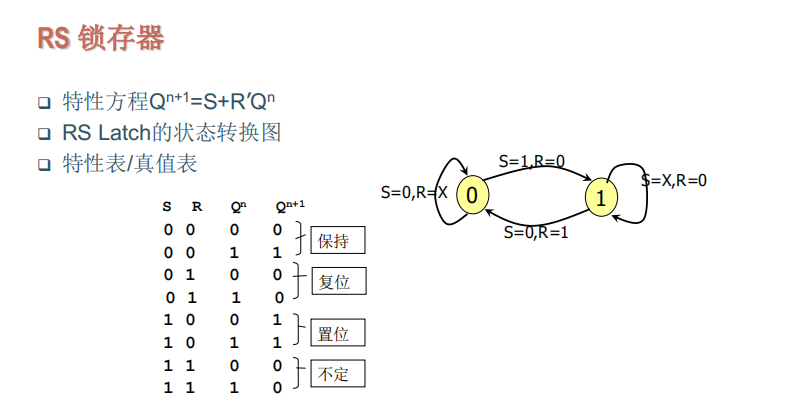

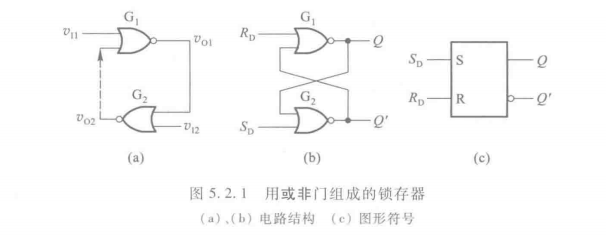

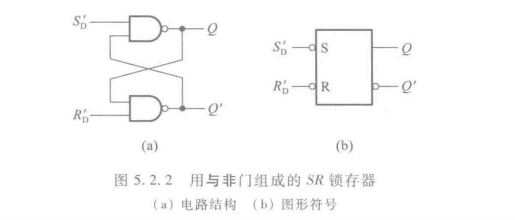

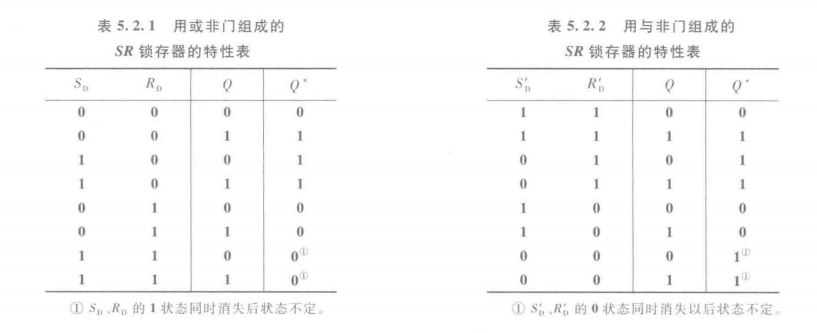

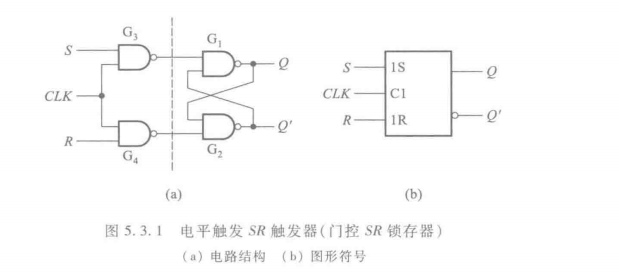

SR锁存器

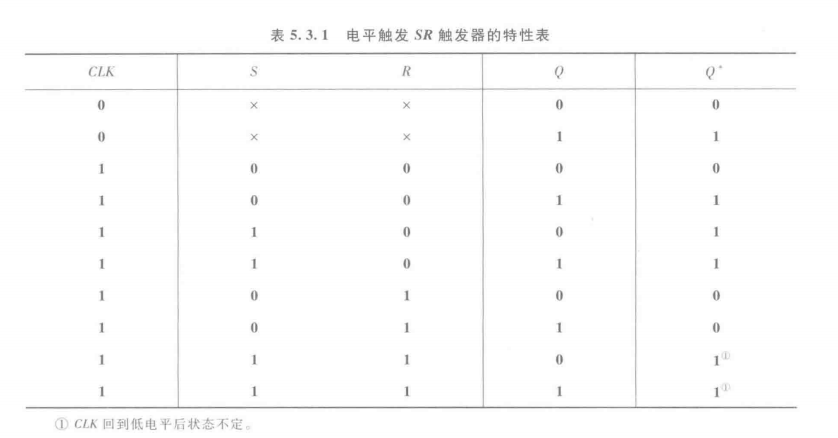

电平触发器

- 只有在clk信号为高电平时才会改变输出

- 缺陷:抗干扰能力差

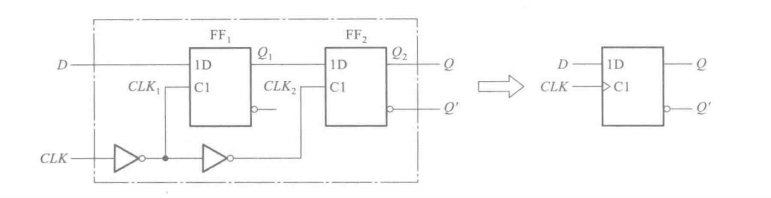

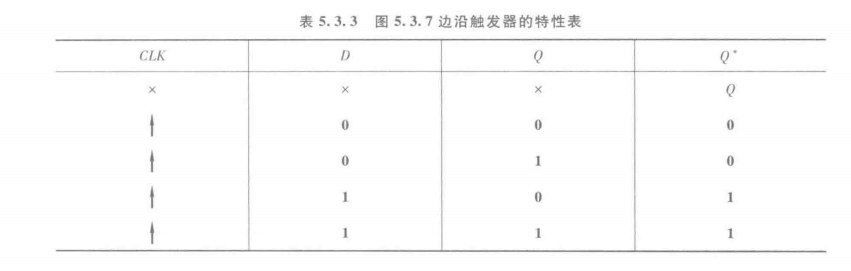

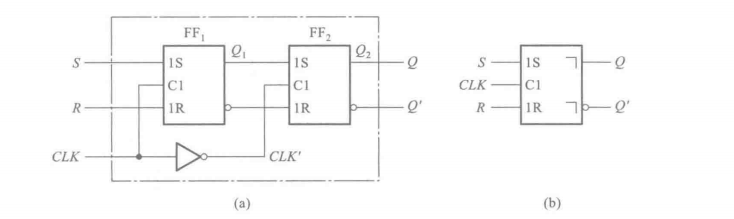

边沿触发器

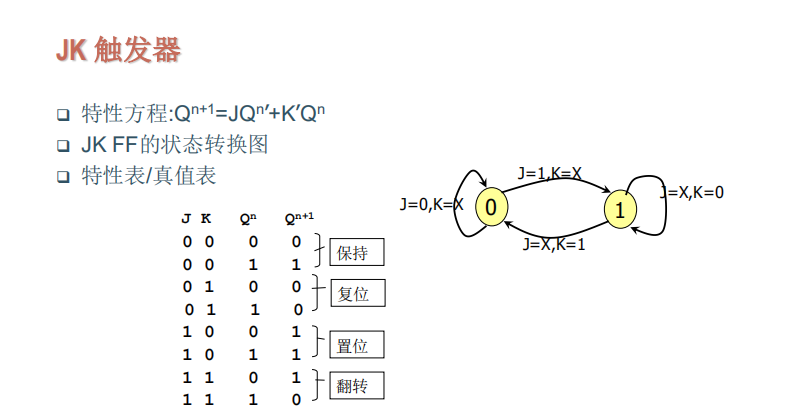

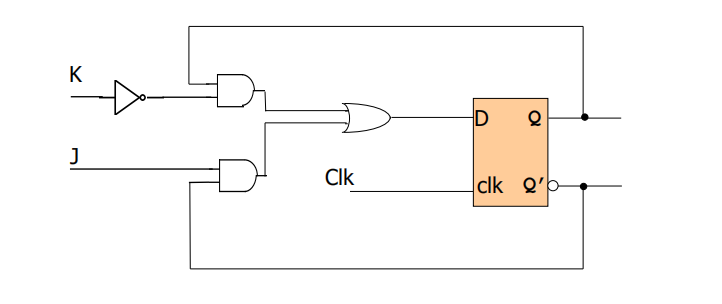

D触发器实现JK触发器

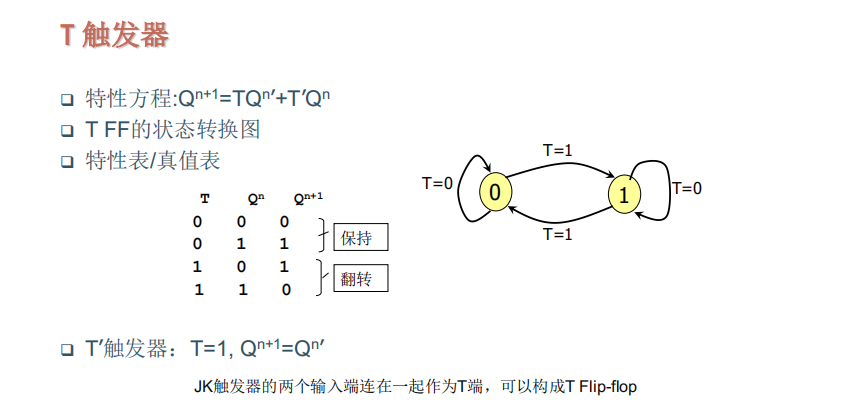

RS,T触发器都可以用JK触发器转化

触发器动态特性

- 建立时间

- 保持时间

- 传输延迟时间

- 最高时钟频率

时序电路

时序逻辑电路类型

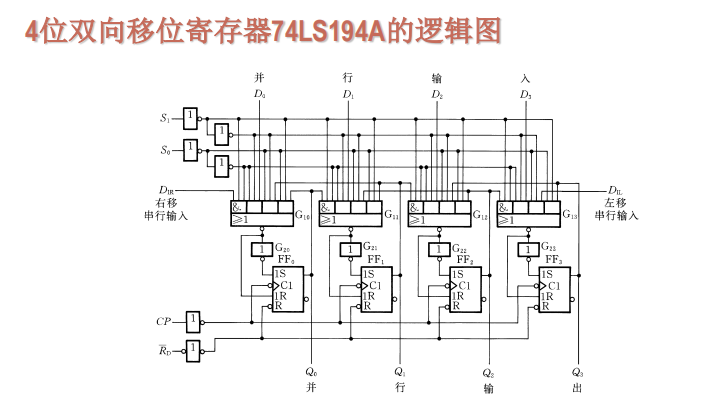

移位寄存器

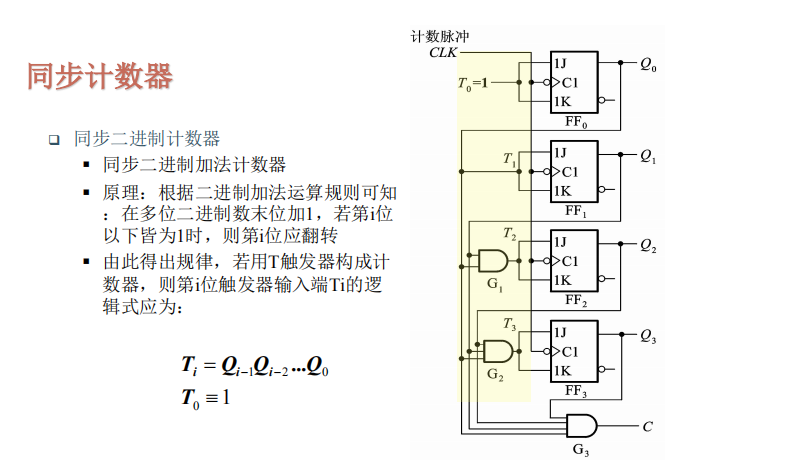

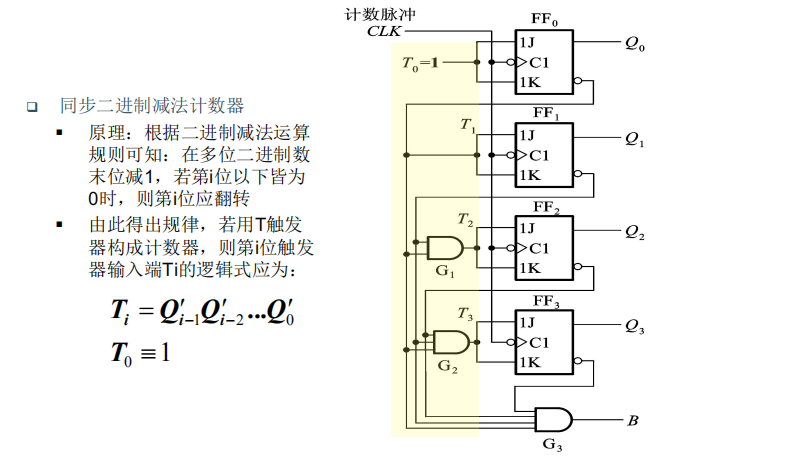

计数器

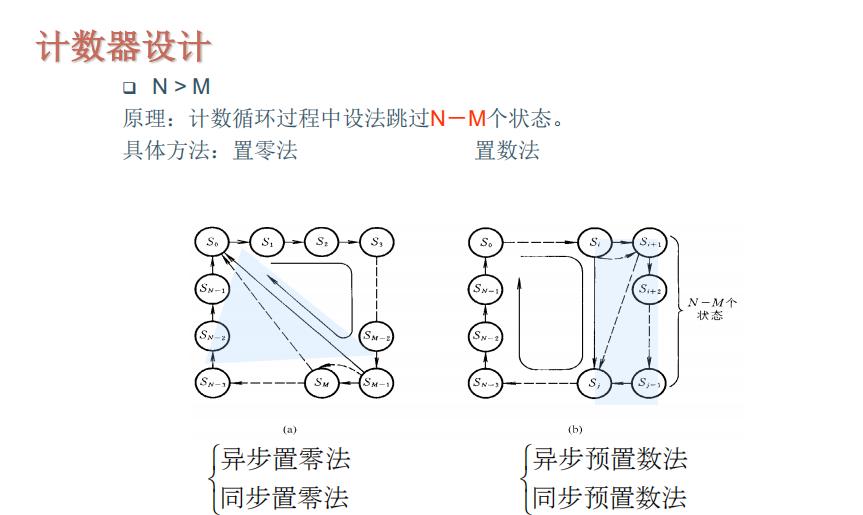

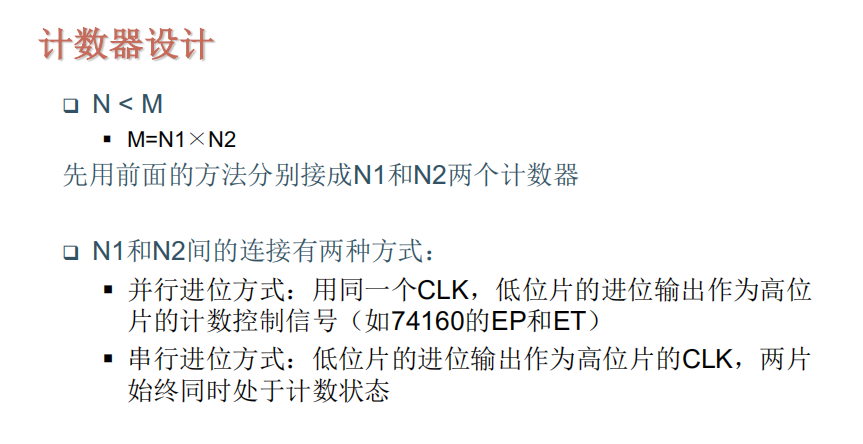

计数器设计

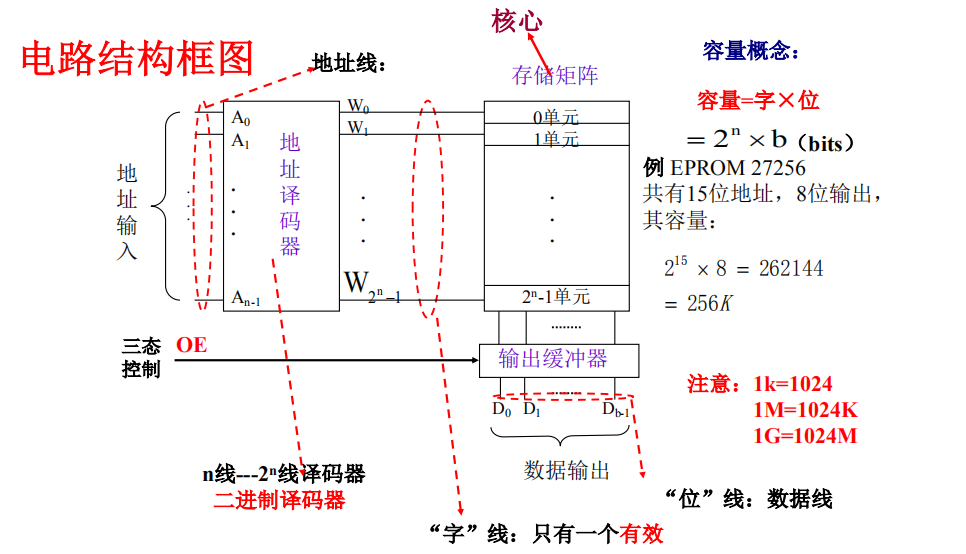

存储器与可编程逻辑阵列

只读存储器ROM

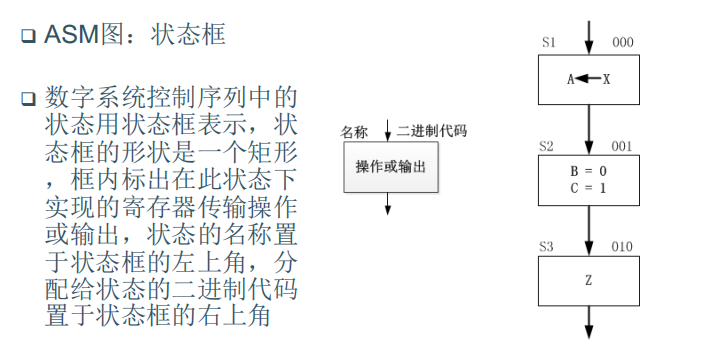

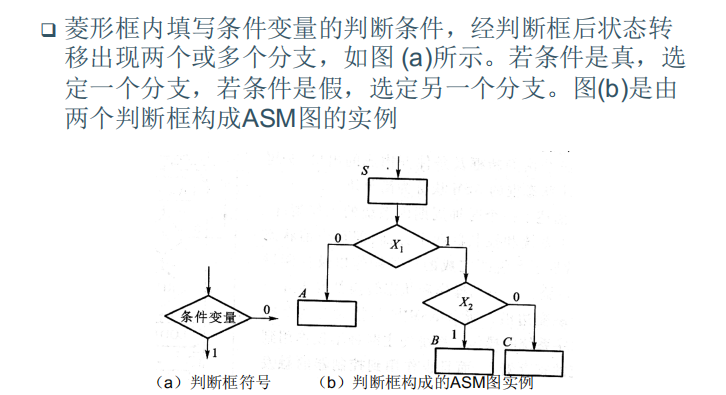

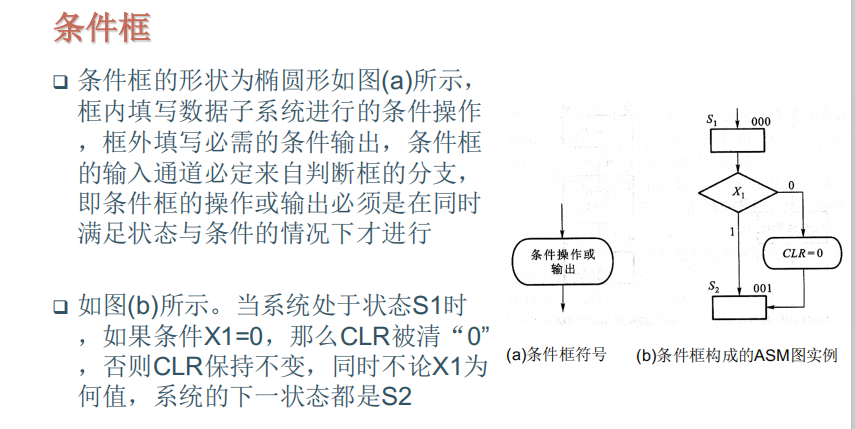

控制器

控制器设计基本方法

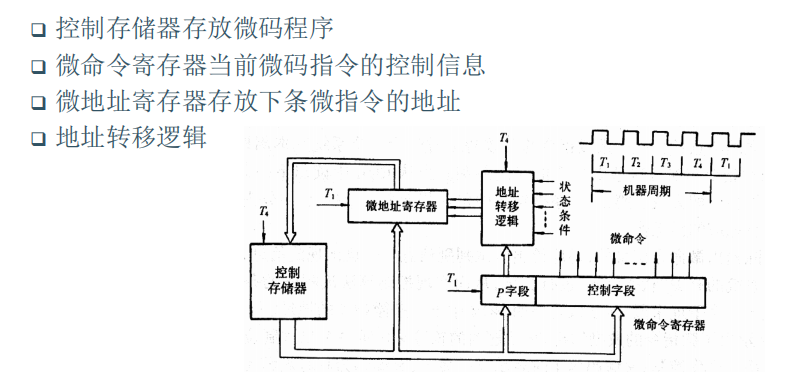

微程序控制器

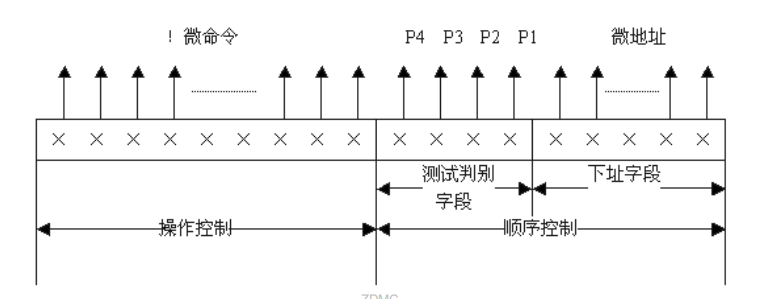

微命令

- 微指令除给出微命令信息外,还给出测试判别信息

- 微指令中还包含一个下址字段,该字段将指明存储器中下一条

微指令的地址 - 微程序是由若干条微码指令组成的序列

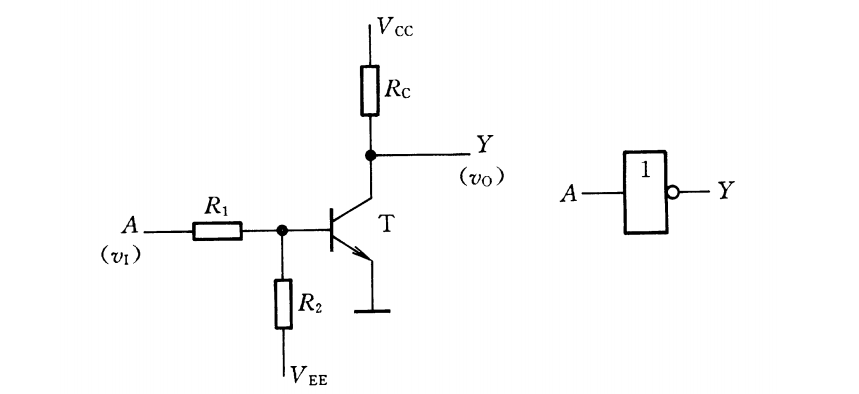

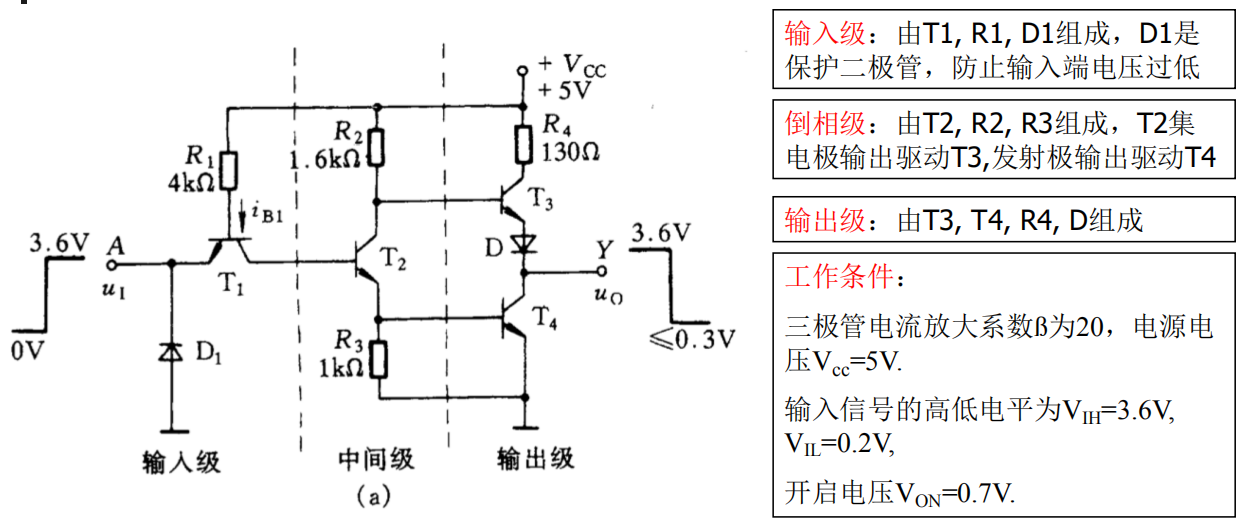

TTL电路

三极管非门

TTL反相器

CMOS

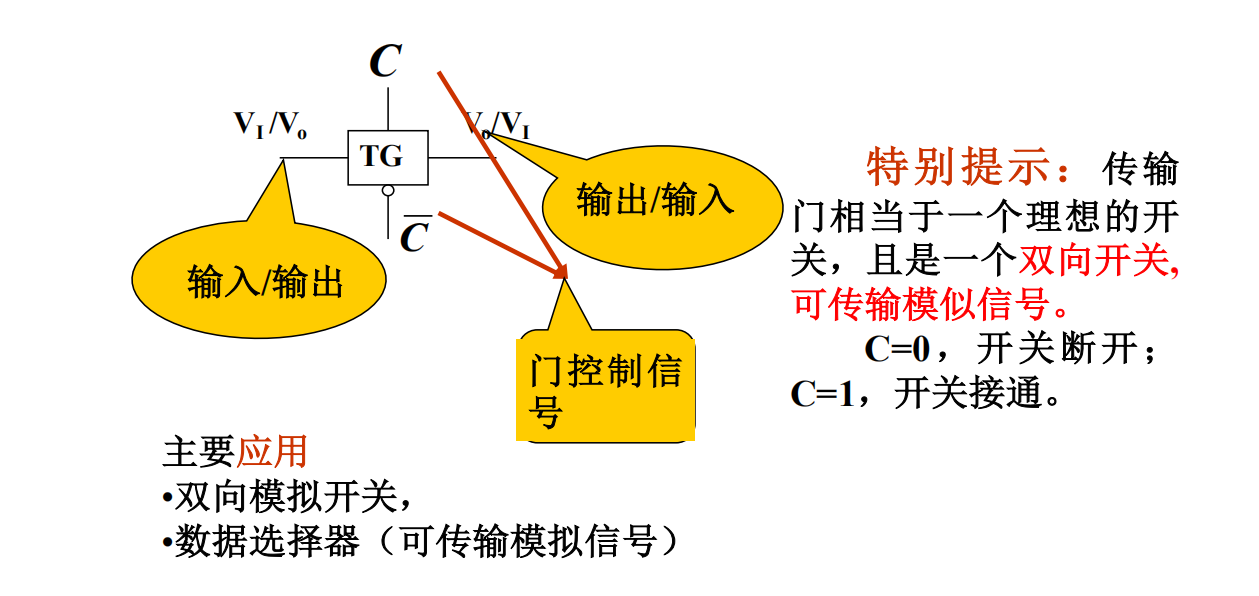

传输门

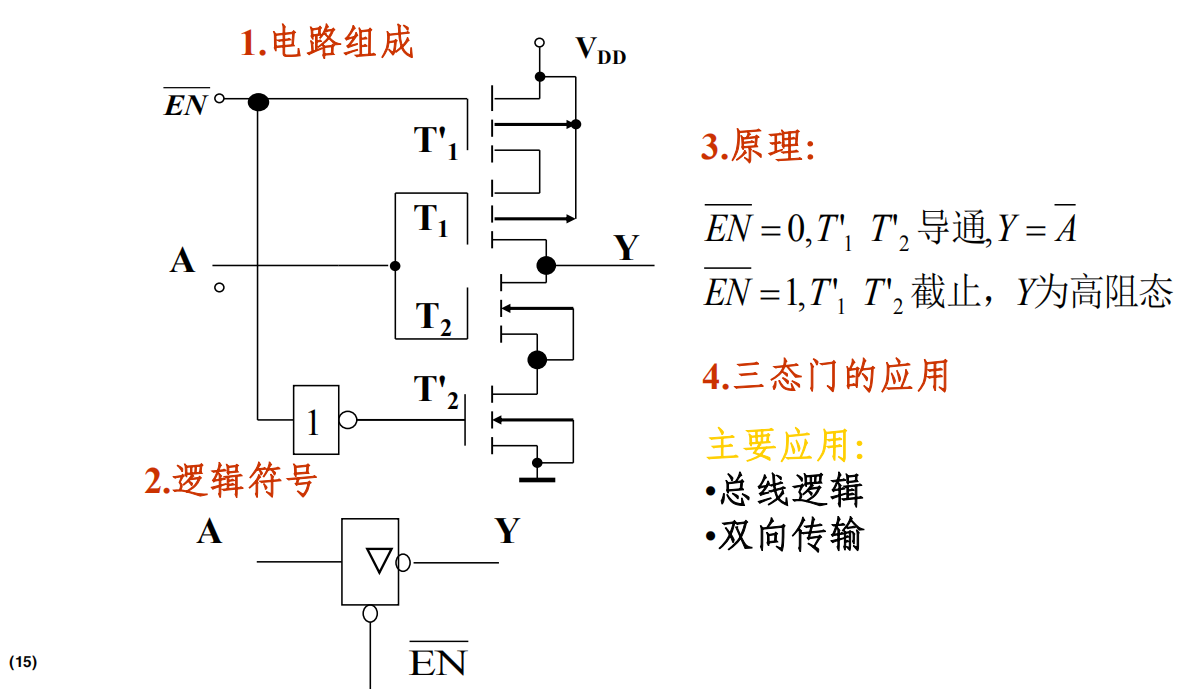

三态门

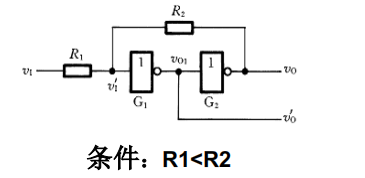

CMOS1和TTL电路最大区别,TTL电路输入端接大电阻变为高电平输入

脉冲电路

施密特电路

- 正向阈值电压

- 负向阈值电压

- 特点:滞后特性

作用:

- 波形变换(整形),抗干扰能力强

- 用于脉冲鉴幅

单稳态电路

微分电路

积分电路

多谐振荡器

对称式

非对称

环形震荡器

集电极开路门电路(OC门)

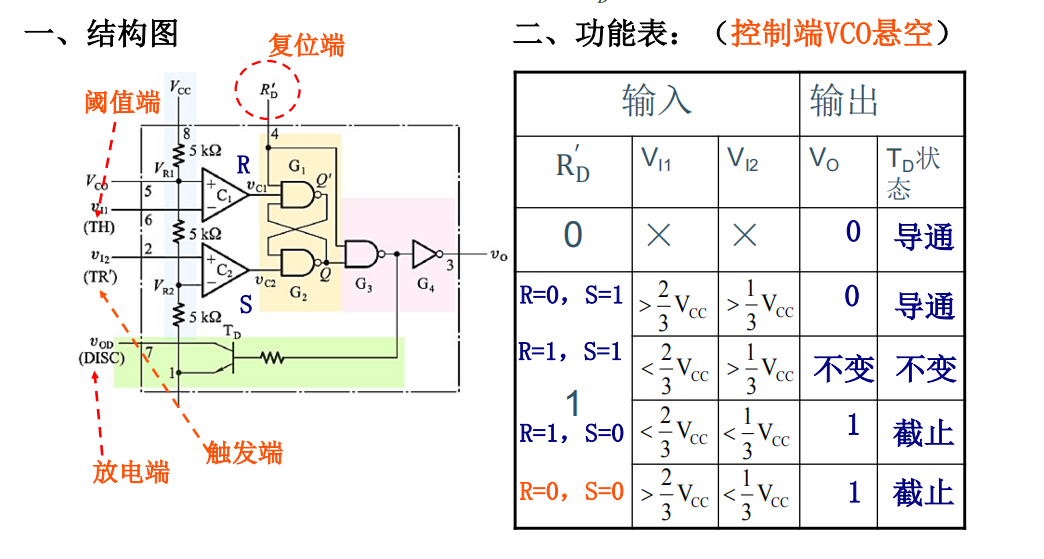

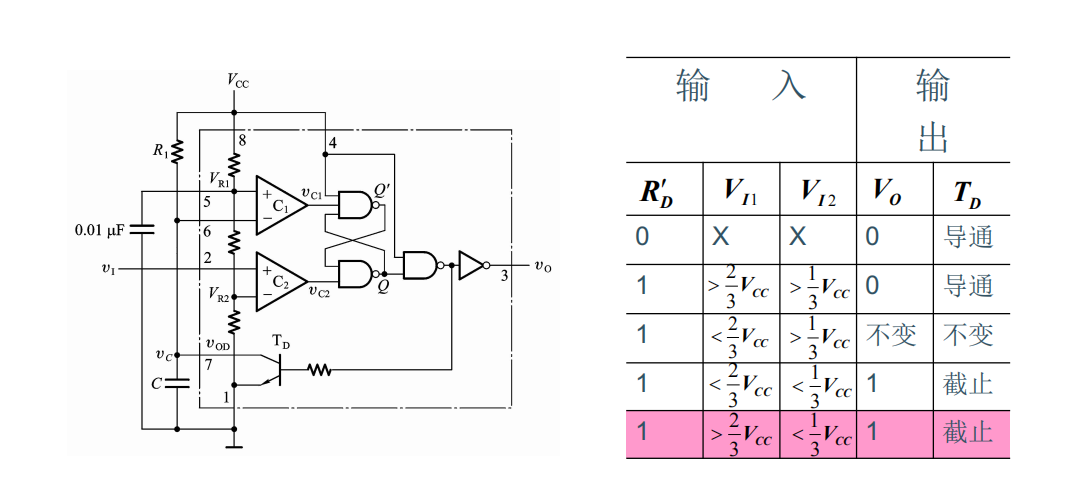

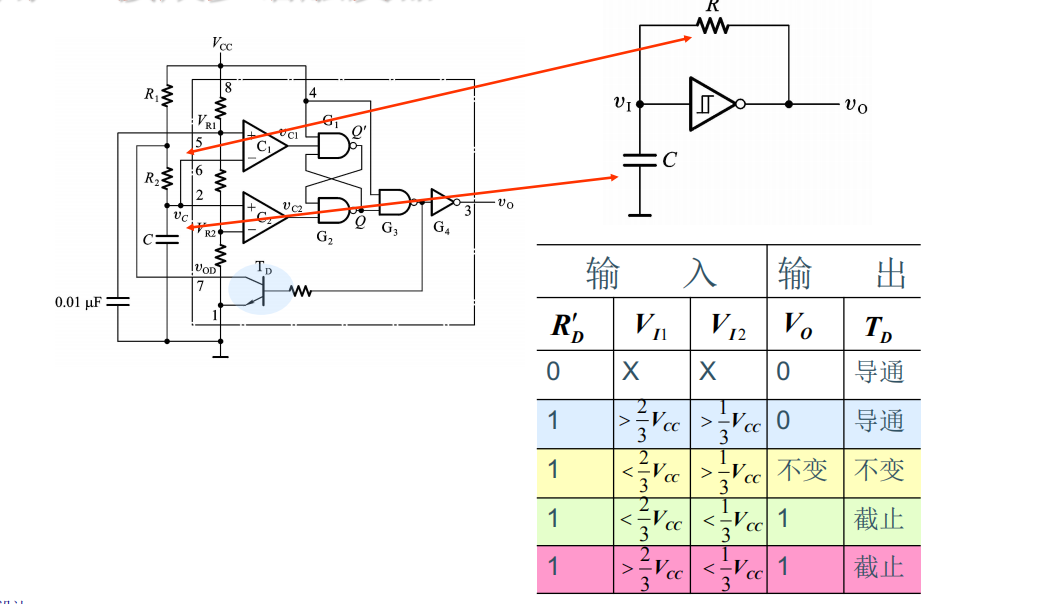

555定时器

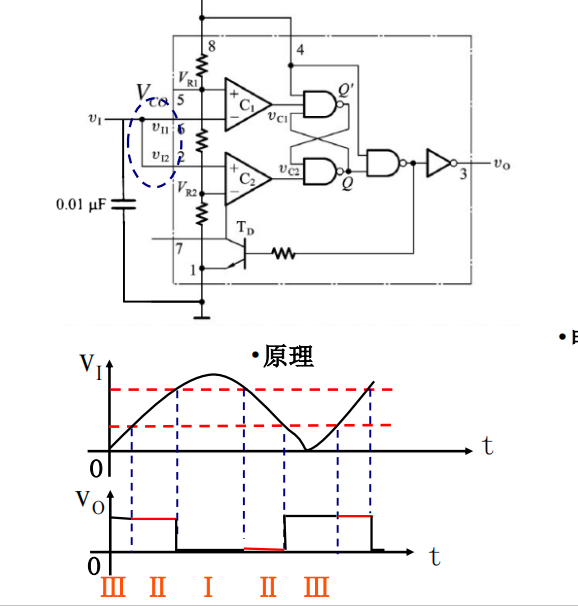

555做施密特触发器

555做单稳态

555做多谐振荡

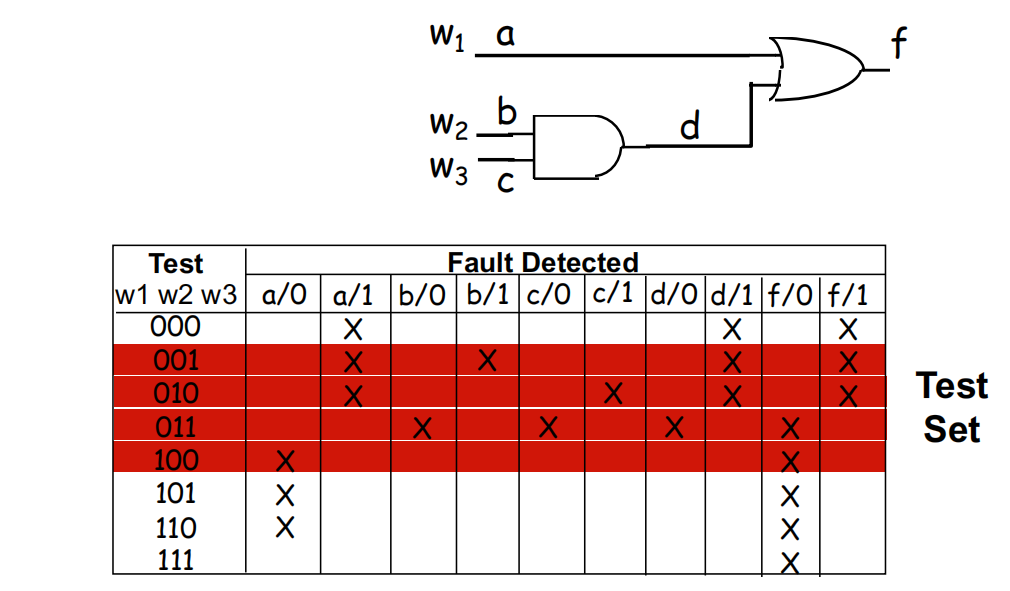

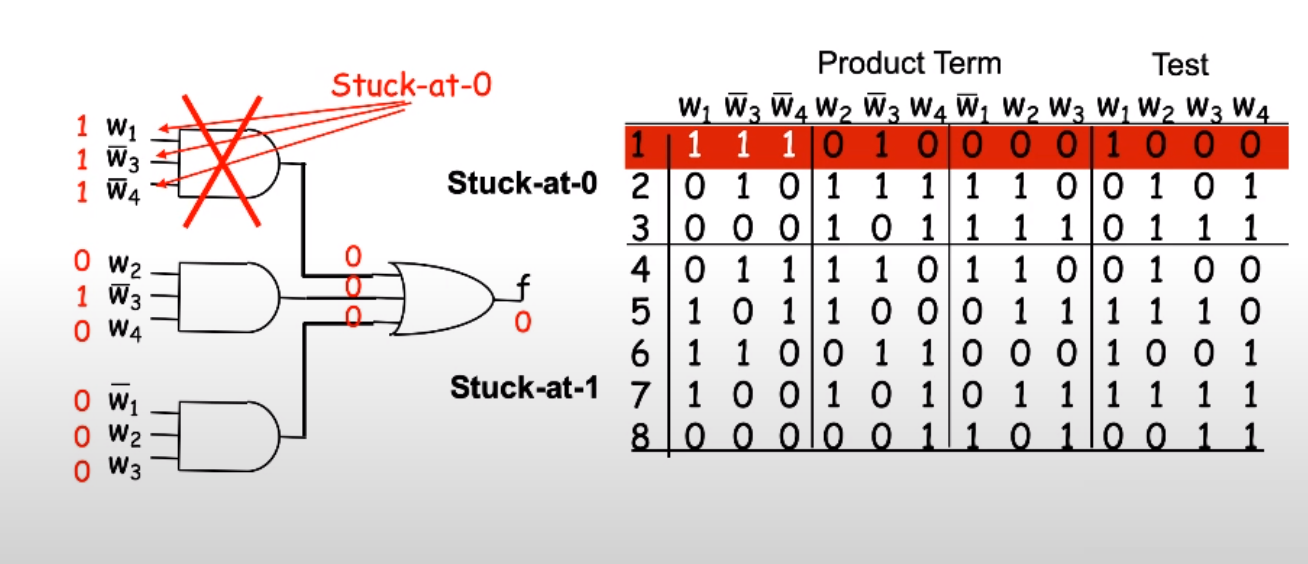

测试

SA1&SA0

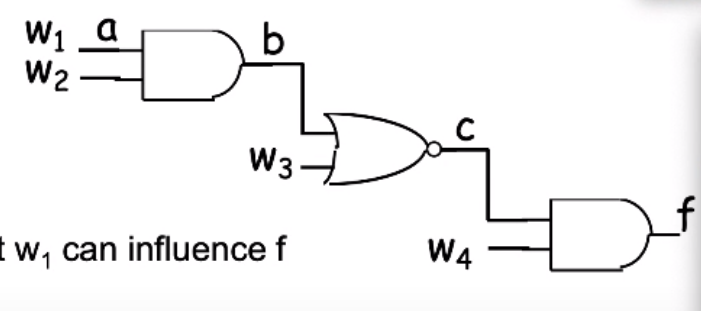

路径敏化

只考虑单个输入变化,其他输入固定,让门退化,与门输入1,或门输入0

可以测试

路径敏化可以一组输入测试多个故障

树型结构

时序电路测试

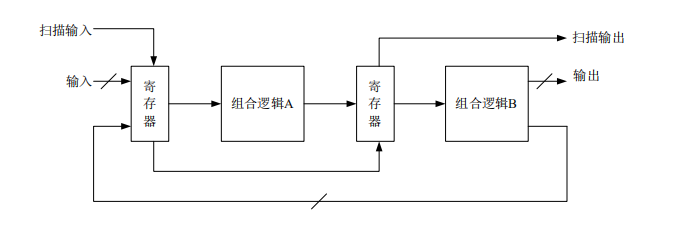

扫描测试

加入多路选择器把内部状态逐级传递出来

在测试时钟的控制下通过扫描输入(ScanIn)引线输入逻辑模块 A(和/或 B)的

激励向量并将其移入寄存器。

激励被加到逻辑模块的输入并传播到它的输出。通过产生一个系统时钟事件把它

的结果锁存到寄存器中。

寄存器中的结果通过扫描输出(ScanOut)引线送出电路并与期望的数据进行比较。

此时一个新的激励向量可以被同时输入。

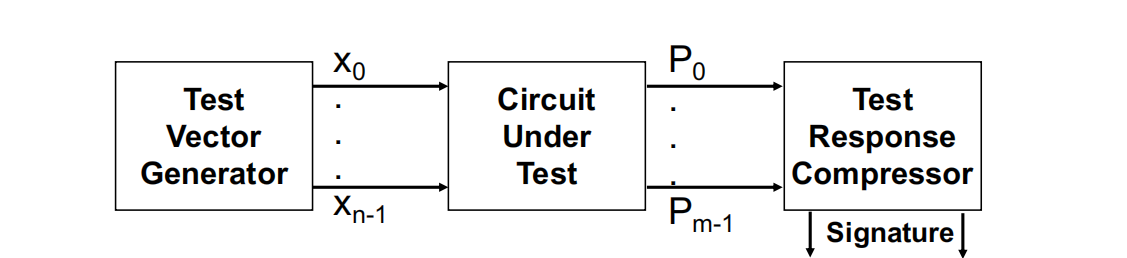

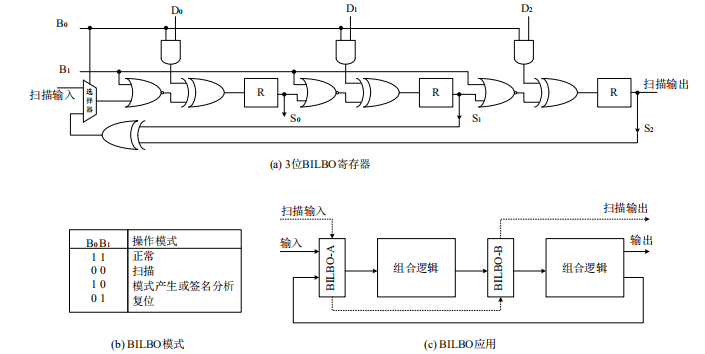

内建自测试

专门测试

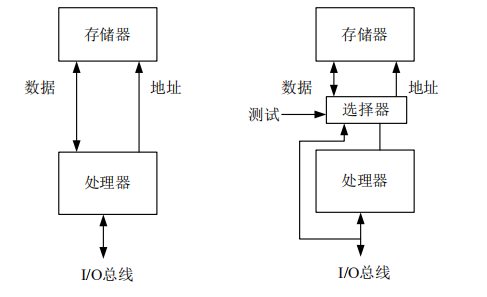

微处理器

什么是微处理器?

• 微处理器由一片或少数几片大规模集成电路组成的中央处理器。

• 这些电路执行控制部件和算术逻辑部件的功能。

• 微处理器能完成取指令、执行指令,以及与外界存储器和逻辑部件交换信息等操作,

是微型计算机的运算控制部分。

微处理器的主要结构

冯诺依曼结构

• 将程序存储和数据存储放在同一物理存储空间

• 相同的总线

• 硬件简单

组成

- 输入 INPUT

- 输出 OUTPUT

- 存储器 MEMORY

- 微处理器 CPU

哈佛结构

• 将程序存储和数据存储分别放在不同的物理存储空间

• 不同的总线

• 灵活、速度快

微处理器内部结构

控制单元

指令集

专门执行一些指令集的微处理器

• 利用指令集编写不同的程序完成不同的处理任务

微处理器三个执行步骤

- 取指

- 译指

- 执行指令

微处理器指令集 ISA

- 指令(Instruction)

- 计算机语言里的单词

- 指令集(Instruction Set Architecture)

- 计算机的词汇

- 指令需指明要执行的操作和要使用的操作数

- 机器语言(Machine Language)

- 指令编码为二进制数格式

- 汇编语言(Assembly Language)

- 符号格式表示各种指令

- 基本指令

- 加、减和跳转指令

操作数

- 常数(Constants)和变量

- 寄存器(register)

- 寄存器组(register set) + 寄存器文件(register file)

- 寄存器操作

$$

$ S_0=a,$ S_1=b,$ S_2=c

add $S_0.$S_1.$S_2

addi

$S_0.$S_0.4

# a=a+4

$$

- 立即数是一个16位二进制补码数据

- 范围是[-32768,32767]

MIPS指令格式

R型———三个寄存器操作数格式

• 用于如add和sub指令,有三个寄存器操作数

- R-type Instructions

- R型是寄存器类型(register-type)的缩写

- 32位指令

| op | rs | rt | rd | shamt | funct |

|---|---|---|---|---|---|

| 6bits | 5bits | 5bits | 5bits | 5bits | 6bits |

- 六个数字域

- op,(也称为opcode或操作码),R型指令的opcode为6‘b000000

- rs,rt,源寄存器

- rd,目标寄存器

- shamt,只用于移位操作,其它R型指令,shamt为5’b00000

- funct,(也称为功能码),确定特定的R型操作

- 每个字段为5比特或6比特

I型————两个寄存器操作数格式

• 用于如lw和sw指令,具有两个寄存器操作数和一个16位立即数

- I型是立即数类型(immediate-type)的缩写

| op | rs | rt | imm |

|---|---|---|---|

| 6bits | 5bits | 5bits | 16bits |

- 四个字段

- op,操作码

- rs,源操作数

- rt,如addi和lw用作目标操作数,sw作为另一种源操作数

- imm,源操作立即数

- rs和imm始终用作源操作数

J型———-无寄存器格式

• 有一个26位的立即数,无寄存器

J型是跳转型(jump-type)的缩写

• 此格式只用跳转指令使用。

• 用26位的地址操作数,addr

• 用于指定一个地址

| op | addr |

|---|---|

| 6bits | 26bits |